Projects - No Research Just for Fun

Yart-Yet Another Ray Tracer

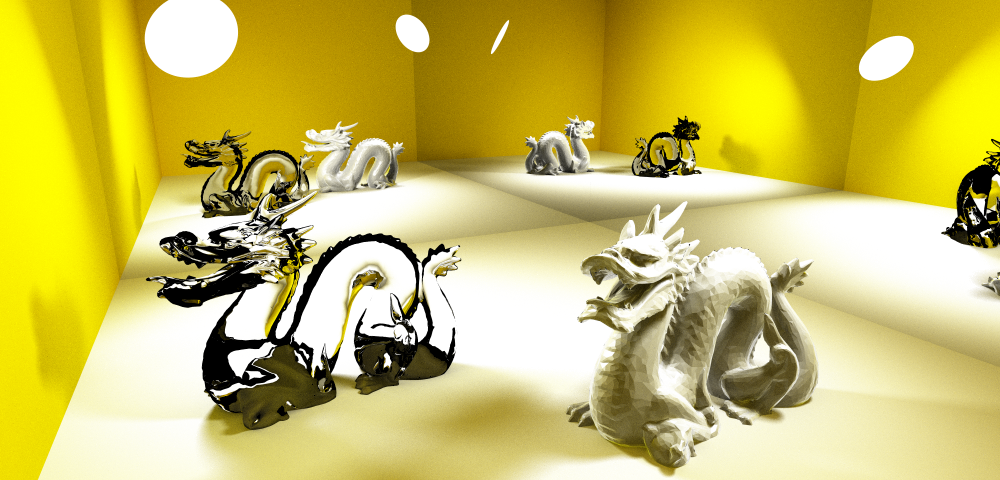

Yart is a simple but powerful ray tracer engine. It reads in a scene description file and parses it. Then it renders the scene and prints the output image. For objects, it supports sphere and triangle mesh. For material, Lambertian, Specular, Refraction and Cook-Torrance BSDF are implemented. To solve the light equation, it can use either direct lighting or bidirectional path tracing. To accelerate the computation, multiple threads and OC-Tree are used.

Sample Images.

Light C-Compiler in C#

Light C-Compiler is an entertainment project for me to practice my programming skill and reach into some deep corners of C language. It implements C99 and works ONLY on Windows 32bits + Visual Studio 2015.

Like many other compilers, lcc divides the whole compilation into 4 stages: lexical analysis, syntax checking, semantic checking and code generation. For the first two stages, three simple tools are developed: RegEx, Lexer and Parserc (see below). The target platform is x86.

Pedestrain Tracker

Pedestrain Tracker is an offline system to track and count pedestrains walking in a video clip. The video is uncaliberated, which means there is no depth information. For detection, we used online boosting with RGB HoG feature. Particle filter is used to tracking multiple targets. The system works well when there is no occlusion however when it is likely to lose the target when there are is occlusion and overlapping. You can find more images and result video clips at the GitHub repo.

MicroPython on FPGA

During the summer 2015, I worked at Imperial College with Johnson under supervision of Prof. Peter Y. K. Cheung. We ported MicroPython to Altera’s DE0-Nano-SoC FPGA. This interpreter can now run not only on ARM Linux, but also on bare-metal (without any OS support, thanks to Johnson). We also extended the interpreter with some modules to support peripherals on the board, and perform communication between HPS and FPGA.

OpenCL@FPGA

This was my undergraduate thesis. I will explore Xilinx’s new OpenCL IDF, SDAccel and try to use it to accelerate the computation on FPGA without writing RTL language such as verilog.